You are hereOpenComRTOS support for Synopsis' ARC processor cores

OpenComRTOS support for Synopsis' ARC processor cores

Altreonic has now developed a first port of its OpenComRTOS Designer™ to the ARC family of processor cores of Synopsis, extending further the range of supported processors. This work was done in the context of the Artemis CRAFTERS project that focuses on the design and programming challenge of developing applications with many- and multicore architectures.

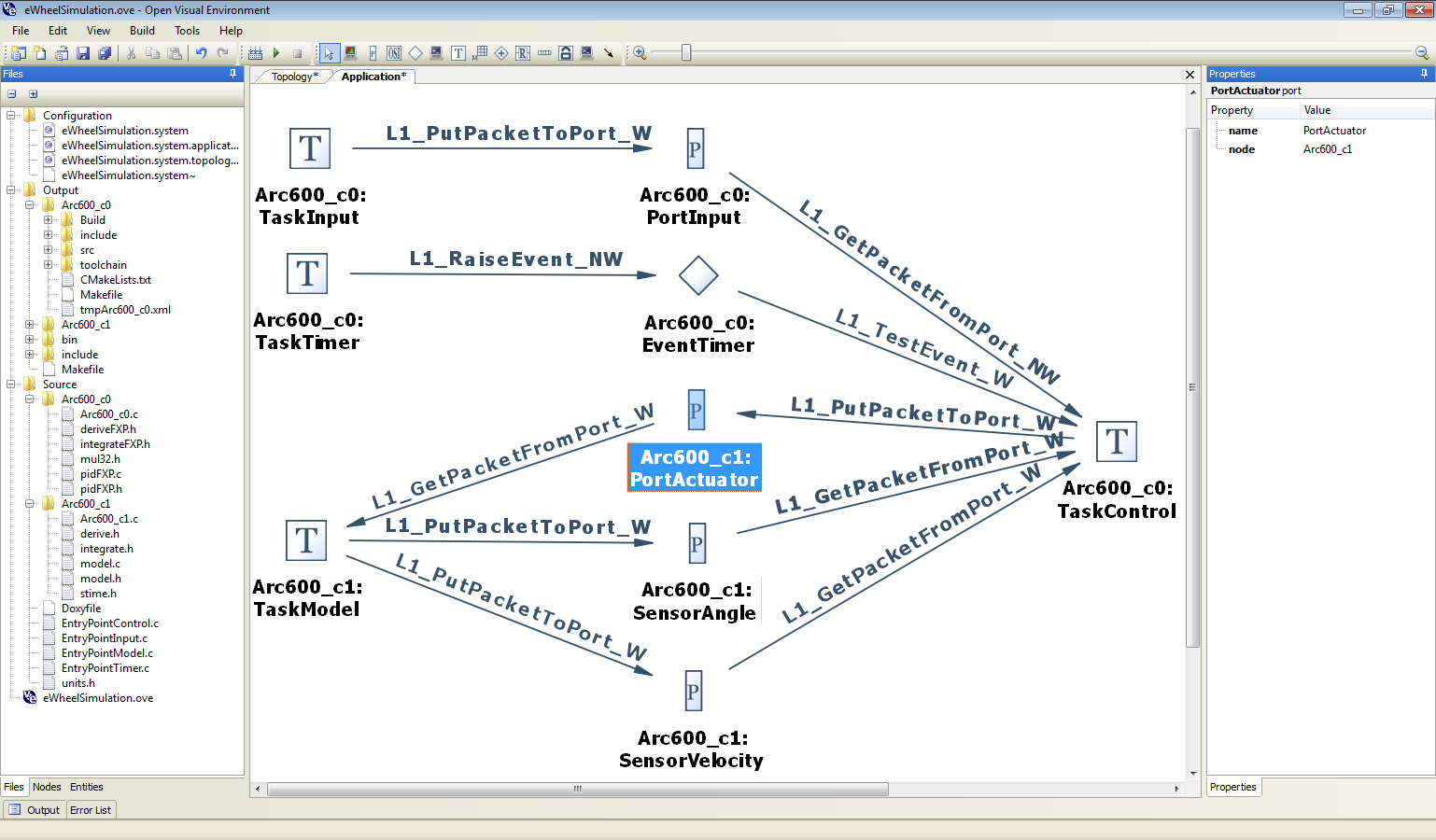

OpenComRTOS has a long history behind it supporting heterogeneous embedded systems in a transparent way going back to 1991. At that time processors were discrete components connected using communication links. Today such architectures are commonly integrated onto a single SoC (System on a chip). Heterogeneous cores are used to optimise performance and power consumption and tens of peripheral I/O blocks provide real-world connectivity. Programming such a system however is not so trivial as the target is complex. OpenComRTOS Designer™ makes that transparent as it is based on a formally developed programming model that separates the application logic from the target's topology. This is achieved by embedded the necessary interprocessor communication as a transparent service in the system layer. Hence the traditional middleware layers do no longer run on top of the operating system but are merged into the operating system layer. A major benefit of this approach and the formally developed architecture is a much reduced code size, typically only 10 KBytes/node.

Another benefit for the application developer is that he can transparently move application code around by recompilation and access peripherals attached to other processing nodes. He can also cross-develop on his PC workstation.

Depending on the services needed, the full kernel requires between 9 and 10 KBytes on the ARC600 (measured on the instruction set simulator, compiled with 0s), this includes the C-runtime library. A typical semaphore loop takes about 2490 cycles (which means 4 context switches and 4 kernel services). Interrupt latency is around 33 cycles to reach the interrupt handler, 103 cycles the reach the Interrupt Service Routine and 660 cycles to reach a waiting processing Task).

Synopsys' DesignWare® ARC® 600 Family of 32-bit RISC processor cores are optimized for embedded applications and DSP tasks where high performance and low power consumption is required. To address a wide range of processing needs, the DesignWare ARC 600 family includes flexible memory options such as single-cycle Closely Coupled Memories (CCMs) for instructions and data, as well as configurable I-cache and D-cache.

The DesignWare ARC 600 family offers a broad range of processor solutions that enable system-on-chip (SoC) designers to create a wide range of embedded microprocessors that are optimized for their specific target applications. These solutions include the DesignWare ARC 601, ARC 605, ARC 610D and ARC 625D.

- Printer-friendly version

- Login to post comments