You are hereOpenComRTOS

OpenComRTOS

Video course by Leslie Lamport on TLA+

Leslie Lamport, the man behind TLA+/TLC, the formal modeling language we used to develop our RTOS kernel has started a series of video lectures on TLA+. If interested in a comprehensive and pragmatic approach to formal modelling, we can only recommend it.

The webpage with a discussion forum is here with the videos here.

Altreonic invited speaker at HIPEAC, Spring CSW in Porto

Eric Verhulst will be speaking at the Spring Computer Systems Week in Porto, presenting at a thematic session on Program transformation and analysis approaches for future computing systems (ProTrans). Title of the presentation: "From CSP to Interacting Entities for programming and modelling". Details can be found here.

Integrated FPGA support with OpenComRTOS Designer

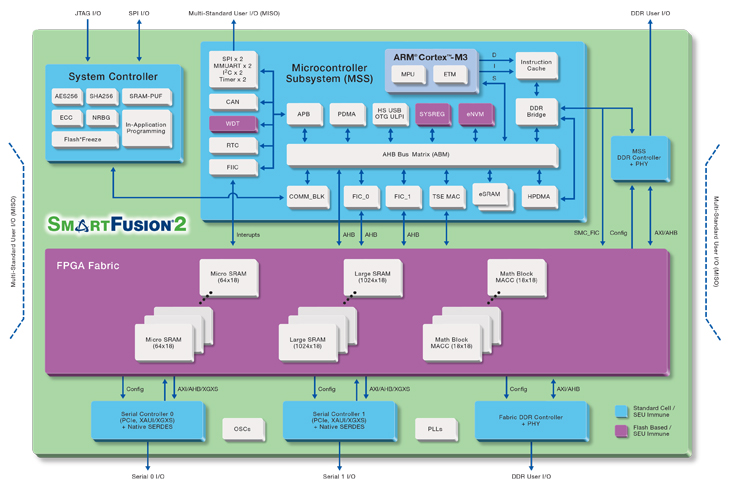

Altreonic announces integrated FPGA support for its multicore/manycore capable OpenComRTOS Designer on Microsemi’s SmartFusion-II.

Advanced chip technology has in the last decade reached a level of integration whereby complete systems can now be made available in a single package. Such Systems On a Chip (SoC) contains often multiple types of processor cores, each specialized for their function, but also smart I/O blocks, on chip networks, caches and program as well as data memory. Recent chips also add FPGA logic blocks.

Advanced chip technology has in the last decade reached a level of integration whereby complete systems can now be made available in a single package. Such Systems On a Chip (SoC) contains often multiple types of processor cores, each specialized for their function, but also smart I/O blocks, on chip networks, caches and program as well as data memory. Recent chips also add FPGA logic blocks.

Since 2005 Altreonic has developed a formally developed runtime system and development environment called OpenComRTOS Designer. Formally developed, it has a typical code size of 5 to 10 KB and supports systems in a fully scalable way. It transparently supports systems with heterogeneous processing nodes as well as heterogeneous communication mechanisms. This makes it suitable for networked, distributed systems as well as for on-chip many/multicore SoC. Board Support packages have been developed for example for TI’s C6678 8-core multi-DSP, Intel’s 48-core SCC as well as for multicore ARM and PPC systems, often replacing traditional memory hungry POSIX-style RTOS.

Today, Altreonic announces integrated FPGA support, demonstrated on Microsemi’s SmartFusion-II. On this chip the user finds a 166 MHz ARM Cortex M3, DMA, I/O blocks and memory as well as a flash programmable FPGA logic. Traditional approaches will treat the FPGA as a co-processing block that is explicitly accessed using dedicated software running on the ARM. In OpenComRTOS tasks synchronise and communicate using so-called intermediate “hub entities” that fully decouple tasks allowing them to be anywhere in the network whereby OpenComRTOS takes cares of the inter-node communication.

ARRL: a novel criterion for trustworthy safety critical systems

Altreonic will present the novel ARRL criterion at the SASSUR (Next Generation of System Assurance Approaches for Safety-Critical Systems) workshop of SAFECOMP2013 on 24th September in Toulouse, France. The paper is co-authored with the Simula Research Lab in Norway (Jose Luis de la Vara) and the University of Antwerp (Vincenzo di Florio).

In summary: ....

New publication in the Gödel Series on real-time and many/multicore

Altreonic is pleased to release a new publication in its Gödel Series, entitled: "QoS and Real Time Requirements for Embedded Many- and Multicore Systems". While the first part is mainly a short summary on real-time scheduling, mostly Rate Monotonic Scheduling and Priority Inheritance support, it already establishes the jump to distributed real-time scheduling as supported in OpenComRTOS.

Altreonic is pleased to release a new publication in its Gödel Series, entitled: "QoS and Real Time Requirements for Embedded Many- and Multicore Systems". While the first part is mainly a short summary on real-time scheduling, mostly Rate Monotonic Scheduling and Priority Inheritance support, it already establishes the jump to distributed real-time scheduling as supported in OpenComRTOS.

Share |

The second part takes a closer look at modern advanced many/multi-core architectures, interrupt latency and inter-core communication measurements and makes the argument that the sharing of the on-chip resources, including the caches, makes it very hard to predict the temporal properties of an application. Rather than rejecting such advanced architectures, the argument is made to adapt the programming model to be able to handle the stochastic spread rather than trying to control it, even if a good design will try to minimise the spread.

Lastly, the bridge is made from Real-Time scheduling towards Quality of Service scheduling of on-chip resources. The connection is made with the specific case of Safety Integrity Levels. Finally, a proposal is made for a new concept that allows to classify components in terms of the assurance they provide for their functional requirements when resources are failing. Under the name ARRL (Assured Reliability and Resilience Level) it provides guidelines for selecting adequate architectures that allow to provide the required services in the presence of several classes of faults. This topic is the subject of on-going and future publications and provides the basis for extensions to the runtime support in OpenComRTOS.

The booklet if freely downloaded from Altreonic's website.

Altreonic HIRES2013 Workshop

Altreonic presents a working paper entitled:

"A Formalised Real-time Concurrent Programming Model for Scalable Parallel Programming",authors Eric Verhulst, Bernhard H.C. Sputh at the Workshop on High-performance and Real-time Embedded Systems(HiRES 2013) January 23, 2013, Berlin, Germany.

Held in conjunction with the 8th International Conference on High-Performance and Embedded Architectures and Compilers (HiPEAC 2013)

Correctness-by-construction

Joseph Kiniry, Professor at the Technical University of Denmark, Copenhagen replied in a lively discussion topic on "GNATprove, integrating theorem provers with software development" in the LinkedIn discussion group "Formal Methods: Specification, Verification, TCG" as follows:

"We find Altreonic's work tremendous. Their pragmatic use of formal methods toward high-end business needs is really a case study in how to do things right and communicate ones results to industry and the academic community. We, too, believe that there is too much emphasis on post-design validation (and, rarely, verification) and believe that a pragmatic correctness-by-construction approach that appreciates and leverages existing quality development practices is the way forward." (quoted with permission).

Altreonic joins Artemis CRAFTERS project

Altreonic is partner in a new Artemis EU project, whose Kick-Off meeting was held in Kopenhagen on 13 to 15 June 2012. Called CRAFTERS (ConstRaint and Application driven Framework for Tailoring Embedded Real-time Systems) it brings together 26 partners covering from EDA vendors, semiconductor designers and manufacturers, software tool vendors, industrial users as well as academia.

Altreonic's product range and roadmap is fully in line addressing the CRAFTERS challenges and will focus on extending OpenComRTOS Designer with dynamic resource scheduling capabilities. Given the abundancy of hardware resources on modern multicore chips, research is focusing on dynamic resource scheduling, whereby a resource is not just CPU time but can also be any of the hardware capabilities. This is using an extended version of the distributed priority inheritance algorithm in OpenComRTOS. The work includes interfacing with other third party tools and defining requirements for the hardware.

New white paper on real-time challenges programming of advanced multicore chips

Multicore chips are becoming more and more the norm these days. This is an evolution driven by the semiconductor advances that allow to put more and more logic on the same die. In addition, as all is on a single die, communication between cores can be speedy and low power as no off-chip I/O is necessary. Nevertheless programming these chips, especially for embedded real-time applications is a challenge.

Following the availability of OpenComRTOS on the 48-core Intel SCC chip and the 8-core Texas Instruments C6678, Altreonic can draw some lessons. OpenComRTOS was designed to support such targets transparently and in a distributed real-time context by separating the hardware topology definition from the application topology definition. This provides for portability and scalability. Nevertheless, these modern multicore chips are complex and it still matters where code and data is placed. For more information, read the attached white paper "Hard real-time on multicores: shared resources are the challenge".

The book on the OpenComRTOS project is out. Lessons learned.

The book is now available from Springer and Amazon.

The book is now available from Springer and Amazon.

While published by a scientific publisher, this book is not a purely scientific one. But it shows how the state of the art in science can be applied to a real industrial development with great benefit. It documents (incompletely but sufficiently) the journey of the OpenComRTOS project. This project started out with the goal to see how we could apply formal methods to embedded software development. And because we had a background in a distributed Real-Time Operating System, we decided to use the design from scratch as a target. Not a trivial one as it covers concurrency, protocols, local as well distributed state machines as well as boundary conditions of efficiency, hard real-time capability, scalability and other non-functional requirements. An RTOS is however a suitable and grateful target as it is the key layer between hardware and application software.