You are hereVirtuosoNext

VirtuosoNext

New article in Science of Computer Programming magazine

Hubs for VirtuosoNext: Online Verification of Real-Time Coordinators

The paper is a collaborative effort of: Guillermina Cledoua (a), José Proença (b), Bernhard H.C. Sputh (c), Eric Verhulst (c)

(a)HASLab/INESC TEC, Universidade do Minho, Portugal, (b)CISTER, ISEP, Portugal, (c)Altreonic NV, Belgium

Extended version at Zenodo.org

Esevier paper at https://www.sciencedirect.com/

Abstract

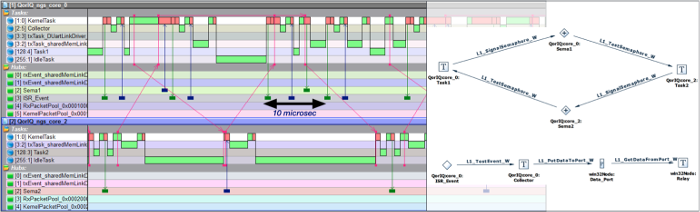

VirtuosoNextTM is a distributed real-time operating system (RTOS) fea- turing a generic programming model dubbed Interacting Entities. This pa- per focuses on these interactions, implemented as so-called Hubs. Hubs act as synchronisation and communication mechanisms between the application tasks and implement the services provided by the kernel. While the kernel provides the most basic services, each carefully designed, tested and opti- mised, tasks are limited to this handful of basic hubs, leaving the development of more complex mechanisms up to application specific implementations.

This work presents a toolset that supports the building of new services compositionally, using notions borrowed from the Reo coordination language, on which the developer can delegate coordination-related duties. This toolset uses a formal compositional semantics for hubs that captures dataflow and time, formalising the behaviour of existing hubs, and allowing the defini- tion of new ones. Furthermore, it enables the analysis and verification of hubs under our automata interpretation, including time-sensitive behaviour via the Uppaal model checker, usable on http://arcatools.org/hubs. We illustrate the proposed tools and methods by verifying key properties on different interaction scenarios between tasks and a composed hub.

Altreonic and LikeAbird join forces

Date: 9th October 2017

Press Release:

Altreonic NV, provider of the unique fault tolerant VirtuosoNext RTOS environment, and

LikeAbird S.L.U., provider of the INAV-IG, the industrial grade Autopilot/Flight Control System Ecosystem for unmanned systems and drones

join forces in combining both technologies in an integrated platform.

LikeAbird is a R&D Think Tank company providing innovative systems, products and solutions in the field of the unmanned (air/land/sea) and robotic industry.

Fault tolerant VirtuosoNext RTOS for ARM Cortex-M microcontrollers

Altreonic has now ported the latest VirtuosoNext Designer to ARM Cortex M-series microcontrollers. The latest version fully exploits the Memory Protection support to provide fine-grain partitioning and allows fine-grain recovery from processor exceptions in a few microseconds at the Task level. This effectively provides fault tolerance for the applications without the system experiencing any significant delay and without having to apply costly hardware redundancy schemes. At the system level, the resilience level is greatly increased at virtually no cost. The economic advantages are significant.

Non-stop hard real-time processing with VirtuosoNext for safety

A fault-tolerant, fully distributed RTOS

Just when you thought there was nothing new anymore in the world of RTOS, the VirtuosoNext RTOS announces seamless fault-tolerance, a milestone for embedded safety and security.

Synopsis: As the world is moving towards "smarter" systems, often embedded, and our life and society is becoming dependent on their uninterrupted operation, fault-tolerance is becoming a prime requirement. Just think about autonomous driving. Will it safely bring you home all the time? In case of a system fault, the reaction time is less than 100 milliseconds. No time for a reboot.

A consequence of the fine-grain space partitioning support in VirtuosoNext is the capability to recover from runtime faults within a few microseconds. The combination of fine-grain concurrency and this fast recovery effectively provides support for non-stop hard real-time processing even when faults occur without a complex and costly system design. VirtuosoNext non-stop capability means that fault-tolerance comes in reach in a cost-efficient manner, as well as in terms of development effort as in terms of compute resources.

New booklet on real-time programming of multicore processors

Altreonic has released an updated version of its "QoS and real-time requirements for embedded many- and multicore systems" booklet. A major chapter was added covering the fine-grain partitioning support of VirtuosoNext on several target processors (Texas Instruments M3, A9, C6678 and Freescale 2080). The paper clearly shows that partitioning support for safety and security can be implemented with almost no penalties for the real-time behaviour. In addition, the code size remains very modest (ranging from less than 10 kbytes to 38 kbytes depending on the target). Download the attached publication for more details.

Altreonic has released an updated version of its "QoS and real-time requirements for embedded many- and multicore systems" booklet. A major chapter was added covering the fine-grain partitioning support of VirtuosoNext on several target processors (Texas Instruments M3, A9, C6678 and Freescale 2080). The paper clearly shows that partitioning support for safety and security can be implemented with almost no penalties for the real-time behaviour. In addition, the code size remains very modest (ranging from less than 10 kbytes to 38 kbytes depending on the target). Download the attached publication for more details.

VirtuosoNext RTOS unleashes the power of Sundance’s OpenVPX DSP board

Together they create a powerful and ultra-high bandwidth processing platform ideally suited for computation and bandwidth-intensive high-reliability and safety-critical applications

Chesham, UK – 21st February 2017. Sundance Multiprocessor Technology Ltd., an established supplier and manufacturer of high performance embedded solutions, has collaborated with Altreonic to port its multicore VirtuosoNextTM Designer embedded RTOS to Sundance’s VF360 3U OpenVPX single board computer (SBC), that integrates a Texas Instruments C6678 Keystone multicore DSP alongside an Altera Stratix® V FPGA.

Read more in the attached press release.

Altreonic selected in EuroCPS open call with VirtuosoNext

Altreonic has been selected in the EuroCPS project to port a Flight Management test application with VirtuosoNext on an avionics platform of Thales. EuroCPS is an European funded project focusing on advanced computing and cyber-physical systems. It gathers several design centers in order to boost and initiate synergies between innovative companies, major CPS-platforms and CPS-competency providers. The specific project with Altreonic is labeled NoFiST (Novel Fine Grain Space and Time Partitioning for a Mixed Criticality Platform) and is a cooperation with Thales TRT. Hereby the abstract:

VirtuosoNext™ Designer ignites TI’s C6678 RoC on Parsec VF360

Altreonic has now ported VirtuosoNext™ Designer to the Texas Instruments’ 8-core C6678 DSP of Sundance’ Parsec VF360 VPX board. The board has 8 floating point DSPs and an Altera Stratix-V on board and is a real single chip signal processing embedded super computer. Running at 1.25 GHz, the eight cores deliver together up to 224 GFlops with a peak bandwidth of 16 Gbytes/s.

Altreonic releases VirtuosoNext v.1.1

Altreonic is proud to announce the release of the version 1.1 of VirtuosoNext™, its high level yet very performant design and programming solution for trustworthy systems development. VirtuosoNext is derived from the formally developed network-centric and distributed OpenComRTOS who’s functionality is inherited.

VirtuosoNext adds the capability to apply fine-grain time and space partitioning when the hardware supports it. VirtuosoNext provides safety measures to trap runtime errors without the system coming to a halt. The approach separates the code in a trusted zone (managed by the VirtuosoNext kernel) and an untrusted zone (executing application tasks). Contrary to traditional hypervisor approaches, the code size and performance penalty is minimal safeguarding the real-time response of a traditionally unprotected RTOS as standard priority based preemptive scheduling is maintained.

VirtuosoNext (protected mode) was initially disclosed in April 2015 This new release has also restructured the code resulting in even lower code sizes. On the ARM-M3, the VirtuosoNext kernel measures between 8 to 11.5 Kbytes. On the ARM A9, the kernel measures between 15 to 22 Kbytes.

Supported processors are ARM M3/M4/R4/R5 and the A7/A9/A15 processor family. The user has the option to enable the protection on specified processing nodes in his distributed or manycore target system. VirtuosoNext 1.1 will hence on make the previous and stable OpenComRTOS v.1.6 superseded as its functionality is integrated. The new services and improvements added with VirtuosoNext v.1.1 can be consulted in the attached files.

Share |

New booklet on ARRL

A new booklet was published in the Gödel Series on the topic of the ARRL (Assured reliability and Resilience Level) criterion. Developed by Altreonic, ARRL is complementary to the traditional Safety Integrity Levels but is domain independent. It aims at a criterion that acts as a contract for the reuse of components and (sub)-systems in the context of trustworthy systems engineering, in particular for safety critical systems. It achieves this by taking faults and how the component or system deals with it, into account. The booklet is available from the download section.

Share |